I. Introducción

Muchas técnicas de control orientadas a procesos industriales continuos que han sido reportadas en los últimos años muestran ventajas en lo referente al desempeño del sistema de control. No obstante, los controladores PID son, sin ninguna duda, los más utilizados en ambientes industriales, debido principalmente a su relación costo-beneficio, la cual es muy deseable en el control de procesos continuos con orientación industrial.

En contraste, los controladores PID convencionales, a causa de su carácter lineal, presentan limitaciones frente a plantas no lineales, casos en los cuales es necesario el uso de controladores que tengan características no lineales en su respuesta. Entre muchas propuestas reportadas en la literatura, una de las opciones que viene atrayendo la atención de los investigadores son los controladores PID difusos directos (FLC PID) [1], debido a que este tipo de controladores reemplaza directamente el PID convencional dentro del lazo de control y hoy en día pueden implementarse en cualquier dispositivo de cómputo actual.

Los controladores PID, en general, tienen en su arquitectura una componente integral que en situaciones de saturación de los actuadores de la planta provocan un fenómeno bien conocido y extensamente estudiado, denominado windup [2]. Este fenómeno es perjudicial para la operación de los controladores, porque se puede ver altamente afectado su desempeño.

Para tratar con este problema en controladores PID convencionales aplicados a procesos continuos han sido propuestas numerosas estrategias, las cuales se denominan anti-windup. Por ejemplo, en [3,4,5] se presenta el análisis de estas estrategias anti-windup aplicadas a controladores PID convencionales, los cuales fueron sintonizados para regular diferentes modelos de procesos continuos; todos fueron validados en entorno de simulación con el fin de mostrar diferentes situaciones típicas en entornos industriales. Así mismo, un par de propuestas sobre mejoras a algunas estrategias clásicas se reportan en [6, 7].

En [8,9,10] se informa sobre estrategias anti-windup basadas en lógica difusa, en las cuales los autores establecen una base de reglas para limitar la cantidad de error que puede acumular el integrador del PID convencional. En [11] se propone una estrategia anti-windup difusa para un sistema de control basado en rechazo activo a perturbaciones; aunque las anteriores propuestas presentan unos resultados adecuados, la implementación de un sistema difuso como estrategia anti-windup puede traer consigo algunos retos en lo referente a la asignación de los parámetros difusos.

Por último, para los FLC se ha informado sobre algunas arquitecturas anti-windup basadas en lógica difusa. Por ejemplo, en [12, 13] no se reportan completamente los elementos del sistema difuso utilizado; por consiguiente, los métodos relacionados en dicho trabajo requieren la sintonización de sus parámetros para conseguir un desempeño adecuado, lo cual puede significar un esfuerzo adicional, situación que no es deseable en los entornos industriales.

Este artículo presenta una propuesta de esquema anti-windup aplicado a controladores FLC PID directos, basado en recálculo y seguimiento, en el cual se establece un método para obtener la constante de seguimiento por medio de las ganancias de escala del FLC. Es decir, en la estrategia propuesta el ajuste del parámetro que permite evitar el windup solamente depende de la información de sintonización del controlador. Adicionalmente, la propuesta se valida en ambiente de simulación a través de un análisis comparativo de tres técnicas anti-windup (integral condicional, reset de la integral y recálculo y seguimiento), en las cuales se midieron su desempeño y robustez frente a perturbaciones utilizando métricas como ITAE e IAE.

Este documento está organizado de la siguiente manera: la sección "Materiales y métodos” menciona brevemente algunas estrategias anti-windup clásicas, se explican las arquitecturas de los FLC PID consideradas y se detalla la estrategia anti-windup propuesta; en la sección "Resultados” se expone el análisis comparativo de diferentes estrategias a través de dos casos de estudio; y por último, se muestran las conclusiones obtenidas después de realizado el análisis y trabajo futuro.

II. Materiales y métodos

A. Estrategias anti-windup para controladores PID

El fenómeno windup en los controladores PID convencionales se presenta cuando se tiene una planta con entrada acotada y la acción de control supera los límites del actuador; por consiguiente, la integral del error se acumula continuamente hasta degradar la respuesta del controlador [14].

El windup en los controladores FLC PID directos se presenta de la misma manera que en los controladores convencionales. Este fenómeno puede afectar de manera más dramática la respuesta de los FLC, debido a que las acciones de control se multiplican por las ganancias de escalamiento; por lo tanto, la acción de control puede llegar a niveles de saturación más fácilmente. A continuación, se presentan algunas estrategias anti-windup clásicas:

1) Integral condicional. Consiste en detener la acumulación del error en el integrador cuando se cumplan ciertas condiciones asignadas por el diseñador. Dos posibles enfoques son:

· Detener la acumulación de error en el integrador cuando la salida del controlador esté saturada.

· Detener la acumulación de error en el integrador cuando el integrador supere unos límites dados.

Cualquiera de estos enfoques permite evitar o por lo menos reducir el efecto del windup en el controlador. Además, son métodos sencillos de implementar, ya que solo es necesario conocer el rango de variación de la acción de control o de la integral, dependiendo del enfoque utilizado. Por otro lado, una desventaja de esta estrategia anti-windup es que no hay garantías de estabilidad y, adicionalmente, el estado del integrador no se modifica, entonces este estado puede afectar la velocidad de respuesta ante cambios de la referencia posteriores a la saturación.

2) Método de reinicio de la integral. Consiste en reiniciar el valor de la integral del error a un valor definido previamente, cuando se alcancen unas condiciones determinadas. La manera más directa para establecer el valor al cual se debe reiniciar el integrador sería utilizando el valor cero, aunque evitaría el efecto de saturación, pues los cambios abruptos en el valor de la integral provocan cambios de la misma naturaleza en la acción de control, por lo tanto, el desempeño del controlador se vería afectado. Teniendo en cuenta lo anterior, en esta estrategia se recomienda el uso de un valor diferente de cero para el reinicio del integrador, lo cual permitirá que el cambio en el valor de la integral no sea tan grande como para afectar significativamente la acción de control. Una de las desventajas de esta estrategia anti-windup es que incluso si se selecciona un valor diferente de cero para el reinicio de la integral, la acción de control se ve afectada en la respuesta temporal, específicamente el tiempo de levantamiento.

3) Recálculo y seguimiento. La estrategia de recálculo y seguimiento fuepropuesta por [2], tiene como principio básico de funcionamiento el recálculo de laintegral a través de un lazo de realimentación, este tiene en cuenta la diferenciaentre la salida del actuador y la acción de control, de tal manera que la salida delcontrolador no supera el límite de saturación del actuador. La ventaja de esteesquema anti-windup es que los cambios en la integral no son abruptos cuando sepresenta saturación, debido a que la retroalimentación permite hacer seguimientode la salida del actuador a través de la ganancia 𝑇𝑡 . Para el cálculo de estaganancia, en [2] se propone que el valor de 𝑇𝑡 sea igual al tiempo integral 𝑇𝑖 ;posteriormente, en [14], esta ganancia se modifica teniendo en cuenta el tiempointegral y el tiempo derivativo mediante: 𝑇𝑡 = √𝑇𝑖𝑇𝑑, buscando que 𝑇𝑡 sea de valormás pequeño que 𝑇𝑖, con esto el valor de la integral cuando se presentasaturación cambia dinámicamente más rápido. El valor de 𝑇𝑡 debe ser más grandeque 𝑇𝑑 para evitar estados no deseados al derivar la señal del error, queprovoquen accidentalmente la activación del anti-windup.

B. Controladores FLC directos

Los controladores PID convencionales son ampliamente utilizados en la industria, debido a su buen desempeño y gran cantidad de métodos de sintonización disponibles en la literatura [7]. Sin embargo, en sistemas no lineales los controladores PID convencionales presentan degradación en su respuesta, principalmente en plantas que requieren de cambios en el set point (SP) [1].

Para este tipo de casos es necesario considerar técnicas de control no lineales que permitan realizar la tarea de control adecuadamente, entre estas se encuentran los controladores FLC PID directos, los cuales reemplazan el controlador PID convencional dentro del lazo de control y utilizan las características no lineales de los sistemas difusos para mejorar el desempeño del sistema. Los controladores difusos en general utilizan tres etapas principales: la fusificación, en la cual se convierten los datos numéricos a valores lingüísticos; la siguiente etapa es una base de reglas que relaciona de manera no lineal las entradas con las salidas; y la última etapa es la defusificación, en la cual se retorna de los valores de los conjuntos difusos a valores numéricos. En los siguientes apartados se presentan dos arquitecturas de controladores FLC PID, ampliamente estudiadas.

C. Arquitectura FLC FPD+I

En la Figura 1 se presenta la arquitectura FLC FPD+I propuesta por [15], la cual tiene como entradas al sistema difuso el error (e) y la derivada del error (∆e); estas señales están multiplicadas por las ganancias de escala GE y GCE respectivamente. Luego, a la salida del sistema difuso, se suma la acción integral incorporando una ganancia de escala denominada GIE; la combinación obtenida a través de la suma es multiplicada por un factor de escala GU, que resulta en la acción de control (U), la cual se expresa en (1).

En el presente documento se implementó como simulación el sistema difuso indicado por el autor, utilizando funciones de pertenencia (MFs) de forma triangular para las entradas e y ⧍e; y empleando tres conjuntos difusos N, Z, P, con un universo de discurso comprendido entre -100 y 100.

Por otro lado, las MFs de salida (u) comprenden 5 conjuntos difusos con forma singleton, -200, -100, 0, 100, 200. En la Figura 1 se puede observar la forma de las MFs consideradas. La base de reglas que relaciona las entradas con las salidas se puede observar en la Tabla 1.

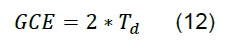

La sintonización se realizó siguiendo la metodología propuesta en [15], en la cual se establecen equivalencias entre las ganancias del PID convencional y las ganancias de escala del FLC, a partir de las siguientes ecuaciones:

D. Arquitectura FLC MHPID

Esta arquitectura FLC MHPID [16] utiliza como entradas al sistema difuso lafusificación de e multiplicada por un factor de escala GE y ⧍e multiplicada por unfactor de escala GCE; la salida U tiene una componente proporcional integral (𝑈𝑃𝐼 )en la cual se realiza la integral de la salida del sistema difuso (salida incremental) multiplicada por un factor de escala GCU y una componente (𝑈𝑃𝐷 ) multiplicada porun factor escala GU (salida absoluta). La acción de control obtenida a la salida delMHPID se puede expresar como se muestra en (6), en la cual el autor consideróponderación en la señal de referencia y derivada de la salida:

La arquitectura FLC MHPID fue implementada en entorno de simulación, considerando las entradas e y derivada de la salida (y), debido a que se parte de un modelo de controlador PID convencional de 2 grados de libertad, con universo de discurso que comprende el intervalo [-1, 1], las MFs de las entradas tienen forma triangular, tal como se observa en la Figura 2. En cuanto a las MFs de la salida, se seleccionan de tipo lineal siguiendo el mecanismo de inferencia Takagi-Sugeno con un universo de discurso definido entre [-2, 2]. La base de reglas que propone es:

La sintonización de la arquitectura FLC MHPID se realizó siguiendo la metodología de [16], en la cual se proponen las siguientes expresiones de equivalencia entre los parámetros del PID convencional y el FLC MHPID:

E. Estrategia de recálculo y seguimiento propuesta

En este documento se propone el uso del esquema clásico de recálculo y seguimiento aplicado a los FLC PID de arquitectura FPD+I y MHPID con el fin de utilizar una estrategia anti-windup simple pero efectiva. En las figuras 3 y 4 se muestra la combinación de las arquitecturas de los PID FLC con la estrategia anti-windup.

En la arquitectura FLC FPD+I se aplicó directamente el esquema de recálculo yseguimiento en el integrador, debido a que el esquema es muy parecido a laarquitectura PID convencional. En (17) se presenta la manera de obtener laconstante 𝑇𝑡 para controladores PID convencionales. Por lo tanto, se propone elcálculo de 𝑇𝑡 en términos de las ganancias de escala del FLC, de tal manera quela estrategia anti-windup solamente dependa de los parámetros de sintonizacióndel controlador de manera comparable con el caso de los PID convencionales.

Las ecuaciones (2) a (5) muestran la manera de calcular las ganancias de escalapara sintonizar el FLC. Entonces, a partir de estas, se pueden expresar losparámetros 𝑇𝑖 y 𝑇𝑑 como:

Siguiendo la propuesta de [14] es posible expresar 𝑇𝑡 de la siguiente manera:

Teniendo en cuenta (17) la ganancia de seguimiento es:

A diferencia del caso anterior, en la arquitectura FLC MHPID la aplicación de la estrategia de recálculo y seguimiento no es directa, debido a que en esta arquitectura no se distinguen las tres componentes PID de manera separada. En la Figura 4 se presenta el esquema anti-windup propuesto para la arquitectura FLC MHPID.

De las ecuaciones (11) a (14) es posible obtener los valores equivalentes del PID convencional en términos de las ganancias de escala del FLC MHPID de la siguiente manera:

Teniendo en cuenta (17), la ganancia de seguimiento es:

Para ambas arquitecturas se observa en el numerador de las ecuaciones (18) y(21) el valor 100. Este es un valor de ajuste necesario, debido a la normalizaciónque tienen los sistemas difusos utilizados para los FLC, con el fin de que el valorde 1/𝑇𝑡 esté dentro del rango de los universos de discurso de las variables decontrol.

III. Resultados

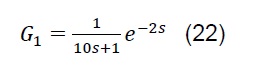

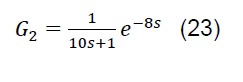

Para evaluar el desempeño de la estrategia anti-windup propuesta se utilizaron dos plantas, representadas por las siguientes funciones de transferencia:

Se seleccionaron modelos de primer orden, debido a que el fenómeno del windup afecta de manera más notable a los sistemas de bajo orden [7]. Se diseñaron controladores en las arquitecturas FLC FPD+I y MHPID siguiendo las metodologías propuestas en [15], [16]. La Tabla 2 muestra las constantes obtenidas para la sintonización de los PID convencionales mediante el método IMC [17] y la Tabla 3 muestra las ganancias de escala para los PID FLC.

Tabla 2. Ganancias de los controladores PID para G1 y G2.

| Kp | Ti | Td | |

| G1 | 4.230 | 11 | 0.909 |

| G2 | 1.346 | 14 | 2.857 |

Tabla 3. Ganancias de escala de los controladores FLC para G1 y G2.

| GU | GE | GIE | GCE | GCU | ||

| FPD+I | G1 | 0.042 | 100 | 9.09 | 90.90 | ---- |

| G2 | 0.013 | 100 | 7.142 | 285.71 | ---- | |

| MHPID | G1 | 2.115 | 1 | ---- | 1.818 | 0.384 |

| G2 | 0.673 | 1 | ---- | 5.714 | 0.096 |

Se realizaron pruebas de las tres estrategias anti-windup tomadas en cuenta en este artículo, con el fin de validar el desempeño del esquema de recálculo y seguimiento aplicado a controladores FLC PID. Se consideró un cambio en la referencia con el propósito de provocar la saturación del actuador cuyos límites se establecieron entre [-10, 10]; posteriormente se introdujo una perturbación para medir el desempeño de las estrategias anti-windup.

En el caso en que se consideró el modelo G1 controlado tanto por la arquitectura FPD+I como por MHPID se presentan comportamientos similares en la respuesta al paso y al cambio en la referencia, en t=400 segundos se introduce una perturbación tipo escalón tal como se muestra en las Figuras 5 y 6.

Tabla 4. Índices de desempeño de los FLC con anti-windup.

| Sin anti- windup | Integral condicional | Reset integral | Recálculo y seguimiento | |||||

| IAE | ITAE | IAE | ITAE | IAE | ITAE | IAE | ITAE | |

| FPD+I | 266 | 3.81e4 | 179.1 | 2.11e4 | 182.1 | 2.14e4 | 157.1 | 1.146e4 |

| MHPID | 259.4 | 3.66e4 | 188.6 | 2.29e4 | 195.6 | 2.36e4 | 170.5 | 1.547e4 |

En la Tabla 4 se muestran algunos índices de desempeño como IAE e ITAE aplicados a los controladores FLC; se puede apreciar que los menores índices los presentan los controladores con anti-windup por recálculo y seguimiento.

En la Figura 7 se observa que el menor esfuerzo de control lo realizan los controladores FLC por recálculo y seguimiento. Adicionalmente se observan las conmutaciones en el esfuerzo de control del FLC MHPID reset integral. En la Tabla 5 se aprecia el índice de desempeño IAU para cada FLC.

Tabla 5. Índice de desempeño del esfuerzo de control IAU de los FLC con anti-windup.

| Sin anti- windup | Integral condicional | Reset integral | Recálculo y seguimiento | |

| FPD+I | 1.04e4 | 4415 | 4752 | 3915 |

| MHPID | 9050 | 4018 | 4259 | 3899 |

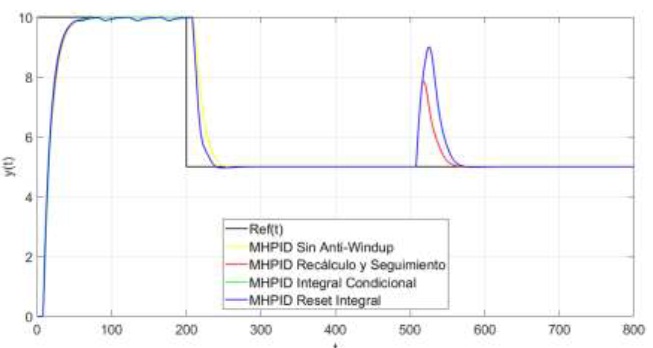

Para las pruebas en las que se empleó el modelo G2, el cual maneja un tiempo muerto 4 veces mayor que G1, se consideran las mismas condiciones anteriores, como cambio en la referencia con el fin de provocar la saturación del actuador y una perturbación en t=500 segundos, lo cual se presenta en las Figuras 8 y 9.

En la Figura 8 se observa que el FLC FPD+I integral condicional muestra un pequeño error de estado estacionario relacionado con el valor del límite superior de la integral con el fin de obtener una acción de control entre -10, 10. En la Figura 9 se aprecia que el FLC FPD+I Reset integral presenta una distorsión en estado estacionario relacionado con el valor de la condicional inicial cuando se realiza el reinicio de la integral.

Tabla 6. Índices de desempeño de los FLC con anti-windup.

| Sin anti- windup | Integral condicional | Reset integral | Recálculo y seguimiento | |||||

| IAE | ITAE | IAE | ITAE | IAE | ITAE | IAE | ITAE | |

| FPD+I | 412 | 8.47e4 | 361 | 7.25e4 | 359.7 | 7.16e4 | 309 | 4.85e4 |

| MHPID | 395.9 | 8e4 | 372.5 | 7.48e4 | 373.8 | 7.55e4 | 328.4 | 5.03e4 |

En la Tabla 6 se presentan los índices de desempeño IAE e ITAE aplicados a los controladores FLC. Se puede apreciar que los menores índices los muestran los controladores con anti-windup por recálculo y seguimiento.

Se observan los esfuerzos de control para cada caso, es posible verificar que son más fuertes para los esquemas de integral condicional y reset de la integral, mientras que la estrategia de recálculo y seguimiento tiene un comportamiento más suave, lo cual se puede apreciar bajo en índice IAU de la Tabla 7.

IV. Discusión y conclusiones

El presente artículo se centró en presentar un análisis comparativo de tres estrategias anti-windup aplicadas a controladores FLC PID, con el fin de evaluar el desempeño del esquema de recálculo y seguimiento propuesto, para el cual la constante de seguimiento se obtiene a partir de los parámetros de sintonización de los FLC. Se consideraron dos casos de estudio para realizar pruebas de las diferentes arquitecturas anti-windup, para los cuales se tuvo en cuenta la respuesta ante cambios en la referencia y perturbaciones.

Los resultados obtenidos después del análisis comparativo entre las diferentes estrategias anti-windup muestran mejores resultados cuando se aplica el esquema de recálculo y seguimiento, debido a que presenta ventajas en aspectos como cambios en la referencia y rechazo de perturbaciones en el sistema de control. Adicionalmente, se observó que la propuesta para obtener la constante de seguimiento es eficaz en sistemas de control PID difusos, puesto que la respuesta de los sistemas trabajados tiene un desempeño adecuado. Debido a esto y a la simplicidad en el cálculo de la constante de seguimiento, la estrategia propuesta puede ser particularmente útil en entornos industriales donde los tiempos y esfuerzos de desarrollo de los controladores deben ser mínimos. En contraste, al utilizar técnicas como integral condicional o reset de la integral es necesario recurrir a pruebas por ensayo y error para lograr obtener el valor de las diferentes variables en la sintonización del integrador y en algunos casos no se logra un comportamiento apropiado.

Por último, como trabajo futuro, la implementación de la técnica propuesta a un proceso continuo de orientación industrial podría enriquecer el tema en cuanto a las consideraciones necesarias en el momento de llevar la arquitectura a un dispositivo de cómputo.

Contribuciones de los autores

Jhon Edisson diseñó e implementó en entorno de simulación el esquema de recálculo y seguimiento aplicado a las arquitecturas de PID difuso consideradas. Jorge Eduardo estableció y llevó a cabo el marco de comparación para evaluar el desempeño del esquema propuesto y las respectivas pruebas dentro del entorno de simulación, y en conjunto se analizaron los resultados y se determinaron las posteriores conclusiones.